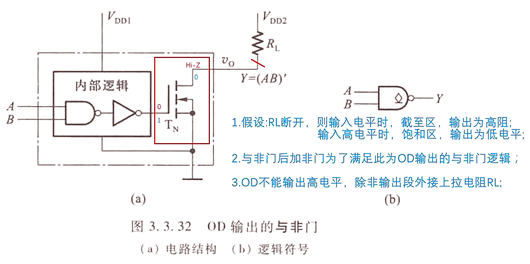

OD門(mén)即漏極開(kāi)路。也就是最右端的MOS管的漏極什么都不接。當(dāng)左端輸入低電平時(shí),...OD門(mén)即漏極開(kāi)路。也就是最右端的MOS管的漏極什么都不接。當(dāng)左端輸入低電平時(shí),右端的MOS管輸出為低電平。然而當(dāng)左端輸入高電平時(shí),由于右端的MOS管漏極處于開(kāi)路狀...

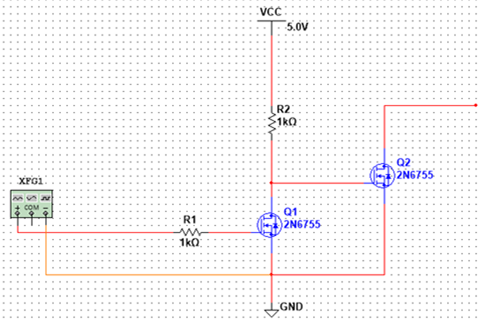

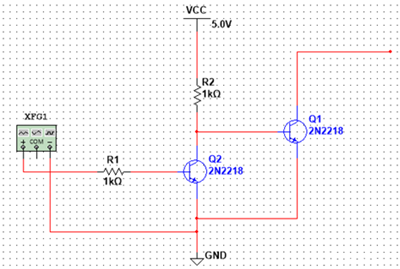

OC門(mén)即集電極開(kāi)路。也就是三極管的集電極什么都不接。當(dāng)左端輸入低電平時(shí),右端...OC門(mén)即集電極開(kāi)路。也就是三極管的集電極什么都不接。當(dāng)左端輸入低電平時(shí),右端的三極管輸出為低電平。然而當(dāng)左端輸入高電平時(shí),由于右端的三極管集電極處于開(kāi)路狀...

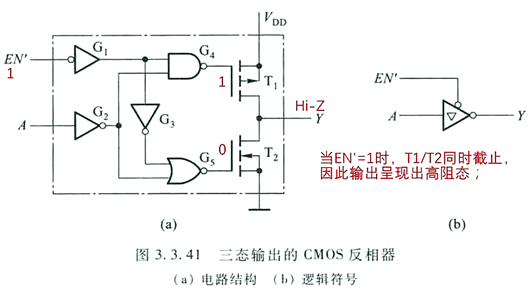

三態(tài)門(mén)輸出電路除了有高低電平兩個(gè)狀態(tài)之外,還有第三個(gè)狀態(tài)--Hi-Z高阻態(tài);三態(tài)門(mén)輸出電路除了有高低電平兩個(gè)狀態(tài)之外,還有第三個(gè)狀態(tài)--Hi-Z高阻態(tài);

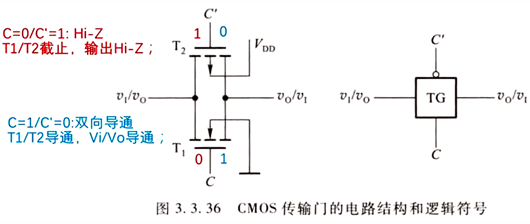

傳輸門(mén)-概念 可當(dāng)作模擬開(kāi)關(guān),用來(lái)傳輸連續(xù)的模擬電壓信號(hào);在Verilog門(mén)級(jí)描述...傳輸門(mén)-概念 可當(dāng)作模擬開(kāi)關(guān),用來(lái)傳輸連續(xù)的模擬電壓信號(hào);在Verilog門(mén)級(jí)描述中,類似于:bufif0/bufif1的作用;

在CMOS電路中為了滿足輸出電平變換,吸收大負(fù)載電流以及實(shí)現(xiàn)線與連接等需要,需...在CMOS電路中為了滿足輸出電平變換,吸收大負(fù)載電流以及實(shí)現(xiàn)線與連接等需要,需要將輸出級(jí)電路結(jié)構(gòu)改為漏極開(kāi)路輸出的MOS管,構(gòu)成漏極開(kāi)路輸出(Open-Drain Output...

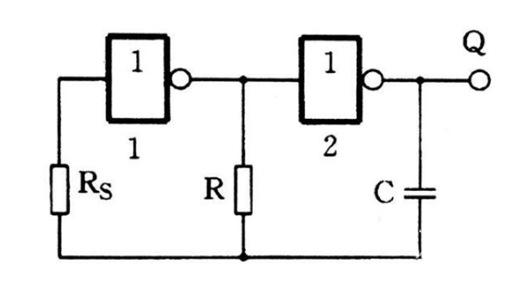

假設(shè)Q為低電平,則非門(mén)2的輸入端為高電平,經(jīng)過(guò)R對(duì)C充電,C的電壓上升,直到非...假設(shè)Q為低電平,則非門(mén)2的輸入端為高電平,經(jīng)過(guò)R對(duì)C充電,C的電壓上升,直到非門(mén)1輸入端的電壓達(dá)到反轉(zhuǎn)電壓,此時(shí)非門(mén)1的輸出變?yōu)榈碗娖剑琎變?yōu)楦唠娖健?/p>