MOS管寄生電容特性測試圖解-KIA MOS管

信息來(lái)源:本站 日期:2021-04-13

寄生電容一般是指電感,電阻,芯片引腳等在高頻情況下表現出來(lái)的電容特性。實(shí)際上,一個(gè)電阻等效于一個(gè)電容,一個(gè)電感,和一個(gè)電阻的串聯(lián),在低頻情況下表現不是很明顯,而在高頻情況下,等效值會(huì )增大,不能忽略。

在計算中我們要考慮進(jìn)去。ESL就是等效電感,ESR就是等效電阻。不管是電阻,電容,電感,還是二極管,三極管,MOS管,還有IC,在高頻的情況下我們都要考慮到它們的等效電容值,電感值。

mos管寄生電容問(wèn)題

mos管寄生電容是動(dòng)態(tài)參數,直接影響到其開(kāi)關(guān)性能,MOSFET的柵極電荷也是基于電容的特性,下面將從結構上介紹這些寄生電容,然后理解這些參數在功率MOSFET數據表中的定義,以及它們的定義條件。

(一)mos管寄生電容數據表

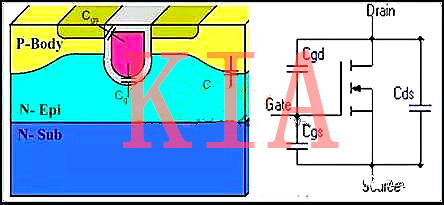

溝槽型功率MOSFET的寄生電容的結構如圖1所示,可以看到,其具有三個(gè)內在的寄生電容:G和S的電容CGS;G和D的電容:CGD,也稱(chēng)為反向傳輸電容、米勒電容,Crss;D和S的電容CDS。

功率MOSFET的寄生電容參數在數據表中的定義,它們和表上面實(shí)際的寄生參數并不完全相同,相應的關(guān)系是:

輸入電容:Ciss=CGS+CGD

輸出電容:Coss=CDS+CGD

反向傳輸電容:Crss=CGD

(二)mos管寄生電容測試

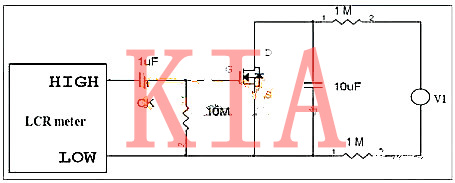

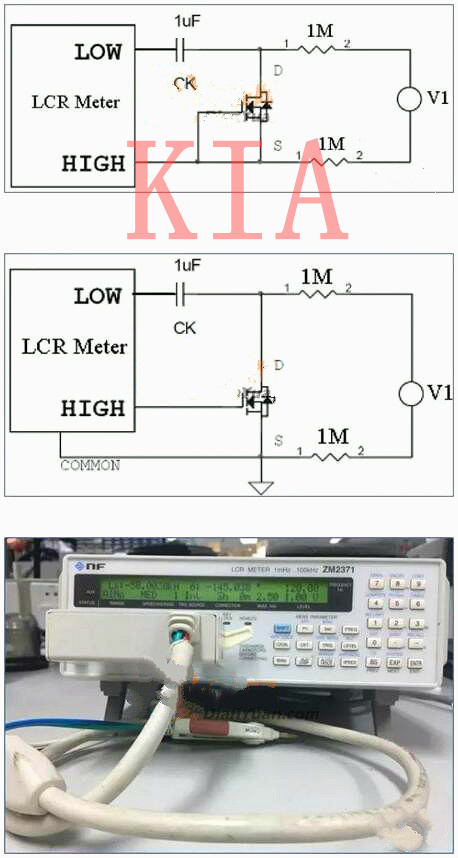

mos管寄生電容測試的條件為:VGS=0,VDS=BVDSS/2,f=1MHz,就是使用的測量電壓為額定電壓的一半,測試的電路所下圖所示。

(a) Ciss測試電路

(d) 標準的LCR

圖2:寄生電容測試電路

mos管柵極的多晶硅和源極通道區域的電容決定了這些參數,其不具有偏向的敏感度,也非常容易重現。

溝槽型功率MOSFET的寄生電容和以下的因素相關(guān):

1、溝道的寬度和溝槽的寬度

2、 G極氧化層的厚度和一致性

3、溝槽的深度和形狀

4、S極體-EPI層的摻雜輪廓

5、體二極管PN結的面積和摻雜輪廓

高壓平面功率MOSFET的Crss由以下因素決定:

1、設計參數,如多晶硅的寬度,晶胞斜度

2、柵極氧化層厚度和一致性

3、體水平擴散,決定了JFET區域的寬度

4、體-EPI和JFET區域的摻雜輪廓

5、柵極多晶硅摻雜通常不是一個(gè)因素,由于其是退化的摻雜;JEFET區域的寬度,JFET輪廓和EPI層摻雜輪廓主導著(zhù)這個(gè)參數。

高壓平面功率MOSFET的Coss由以下因素決定:

1、所有影響Crss參數,由于它是Coss一部分

2、體二極管PN結區域和摻雜輪廓

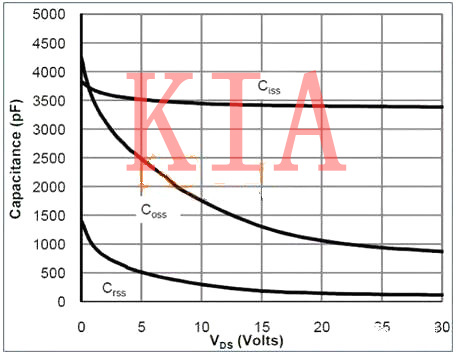

(三)mos管寄生電容的非線(xiàn)性

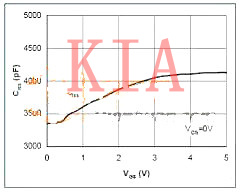

MOSFET的電容是非線(xiàn)性的,是直流偏置電壓的函數,圖3示出了寄生電容隨VDS電壓增加而變化。所有的MOSFET的寄生電容來(lái)源于不依賴(lài)于偏置的氧化物電容和依賴(lài)于偏置的硅耗盡層電容的組合。由于器件里的耗盡層受到了電壓影響,電容CGS和CGD隨著(zhù)所加電壓的變化而變化。

圖3:AON6512電容隨電壓變化

電容隨著(zhù)VDS電壓的增加而減小,尤其是輸出電容和反向傳輸電容。當電壓增加時(shí),和VDS相關(guān)電容的減小來(lái)源于耗盡層電容減小,耗盡層區域擴大。然而相對于CGD,CGS受電壓的影響非常小,CGD受電壓影響程度是CGS的100倍以上。

圖4顯示出了在VDS電壓值較低時(shí),當VGS電壓增加大于閾值電壓后,MOSFET輸入電容會(huì )隨著(zhù)VGS增加而增加。

圖4:輸入電容隨VGS變化

因為MOSFET溝道的電子反形層形成,在溝漕底部形成電子聚集層,這也是為什么一旦電壓超過(guò)QGD階級,柵極電荷特性曲線(xiàn)的斜率增加的原因。所有的電容參數不受溫度的影響,溫度變化時(shí),它們的值不會(huì )發(fā)生變化。

聯(lián)系方式:鄒先生

聯(lián)系電話(huà):0755-83888366-8022

手機:18123972950

QQ:2880195519

聯(lián)系地址:深圳市福田區車(chē)公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關(guān)注”官方微信公眾號

請“關(guān)注”官方微信公眾號:提供 MOS管 技術(shù)幫助