MOS知識分享|CMOS邏輯門(mén)電路干貨解析-KIA MOS管

信息來(lái)源:本站 日期:2020-12-10

CMOS邏輯門(mén)電路是在TTL電路問(wèn)世之后, 所開(kāi)發(fā)出的第二種廣泛應用的數字集成器件,從發(fā)展趨勢來(lái)看,由于制造工藝的改進(jìn),CMOS電路的性能有可能超越TTL而成為占主導地位的邏輯器件。

CMOS電路的工作速度可與TTL相比較,而它的功耗和抗干擾能力則遠優(yōu)于TTL。此外,幾乎所有的超大規模存儲器件,以及PLD器件都采用CMOS藝制造,且費用較低。

早期生產(chǎn)的CMOS門(mén)電路為4000系列,隨后發(fā)展為4000B系列。當前與TTL兼容的CMO器件如74HCT系列等可與TTL器件交換使用。下面首先討論CMOS反相器,然后介紹其他CMOS邏輯門(mén)電路。

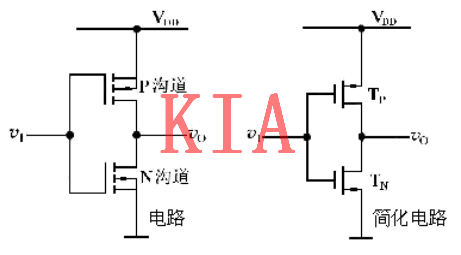

MOSFET有P溝道和N溝道兩種,每種中又有耗盡型和增強型兩類(lèi)。由N溝道和P溝道兩種MOSFET組成的電路稱(chēng)為互補MOS或CMOS電路。

下圖表示CMOS反相器電路,由兩只增強型MOSFET組成,其中一個(gè)為N溝道結構,另一個(gè)為P溝道結構。為了電路能正常工作,要求電源電壓VDD大于兩個(gè)管子的開(kāi)啟電壓的絕對值之和,即VDD>(VTN+|VTP|)。

1.工作原理

首先考慮兩種極限情況:當V1處于邏輯0時(shí),相應的電壓近似為0V;而當V1處于邏輯1時(shí),相應的電壓近似為VDD。假設在兩種情況下N溝道管TN為工作管P溝道管Tp為負載管。但是,由于電路是互補對稱(chēng)的,這種假設可以是任意的,相反的情況亦將導致相同的結果。

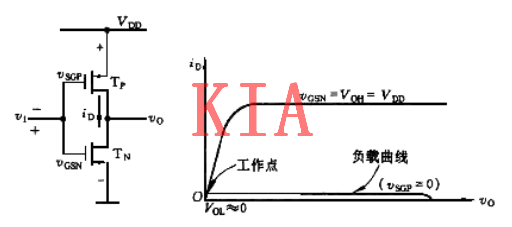

下圖分析了 當V1=VDD時(shí)的工作情況。在TN的輸出特性iD-VDS(VGSN=VDD)(注意VDSN=V0)上,疊加一條負載線(xiàn),它是負載管Tp在VSGp=0V時(shí)的輸出特性iD-VsD。

由于VsGp

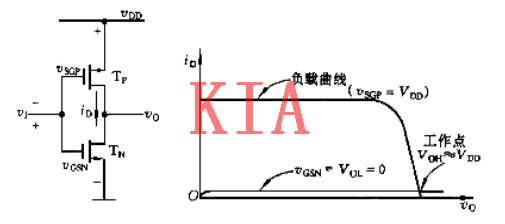

下圖分析了另一種極限情況,此時(shí)對應于V1=0V。此時(shí)工作管TN在VGsN=0的情況下運用,其輸出特性iD-VDs幾乎與橫軸重合,負載曲線(xiàn)是負載管Tp在VsGP=VDD時(shí)的輸出特性iD-VDs。

由圖可知,工作點(diǎn)決定了VO=VOH≈VDD;通過(guò)兩器件的電流接近零值。可見(jiàn)上述兩種極限情況下的功耗都很低。

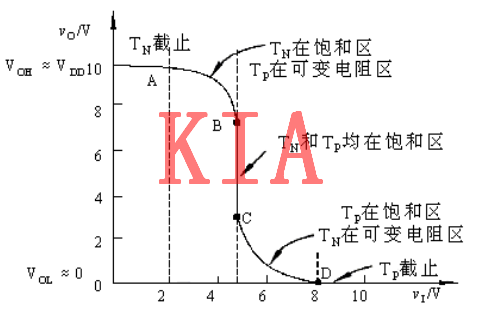

2.傳輸特性

下圖為CMOS反相器的傳輸特性圖。圖中VDD=10V, VTN=|VTP|=VT=2V。由于VDD> (VTN+|VTP|) ,因此,當VDD-|VTp|>vl>VTN時(shí),TN和Tp兩管同時(shí)導通。考慮到電路是互補對稱(chēng)的,一器件可將另一器件視為它的漏極負載。

還應注意到,器件在放大區(飽和區)呈現恒流特性,兩器件之一可當作高阻值的負載。因此,在過(guò)渡區域,傳輸特性變化比較急劇。兩管在V1=VDD/2處轉換狀態(tài)。

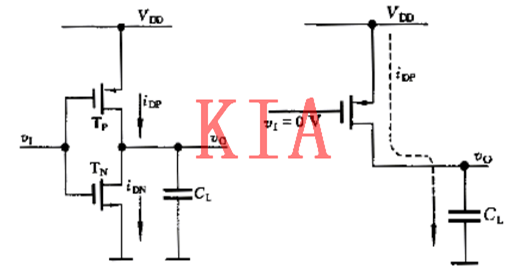

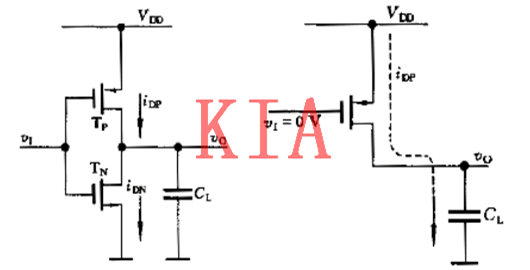

3.工作速度

CMOS反相器在電容負載情況下,它的開(kāi)通時(shí)間與關(guān)閉時(shí)間是相等的,這是因為電路具有互補對稱(chēng)的性質(zhì)。下圖表示當V1=0V時(shí),TN截止,Tp導通,由VDD通過(guò)Tp向負載電容CL充電的情況。由于CMOS反相器中,兩管的gm值均設計得較大,其導通電阻較小,充電回路的時(shí)間常數較小。類(lèi)似地,亦可分析電容CL的放電過(guò)程。CMOS反相器的平均傳輸延遲時(shí)間約為10ns。

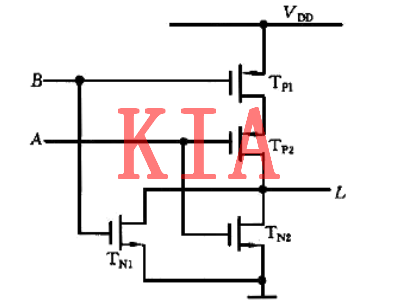

1.與非門(mén)電路

下圖是2輸入端CMOS與非門(mén)電路,其中包括兩個(gè)串聯(lián)的N溝道增強型MOS管和兩個(gè)并聯(lián)的P溝道增強型MOS管。每個(gè)輸入端連到一個(gè)N溝道和一個(gè)P溝道MOS管的柵極。

當輸入端A、B中只要有一個(gè)為低電平時(shí),就會(huì )使與它相連的NMOS管截止,與它相連的PMOS管導通,輸出為高電平;僅當A、B全為高電平時(shí),才會(huì )使兩個(gè)串聯(lián)的NMOS管都導通,使兩個(gè)并聯(lián)的PMOS管都截止,輸出為低電平。

n個(gè)輸入端的與非門(mén)必須有n個(gè)NMOS管串聯(lián)和n個(gè)PMOS管并聯(lián)。

2.或非門(mén)電路

下圖是2輸入端CMOS或非門(mén)電路。其中包括兩個(gè)并聯(lián)的N溝道增強型MOS管和兩個(gè)串聯(lián)的P溝道增強型MOS管。

當輸入端A、B中只要有一個(gè)為高電平時(shí),就會(huì )使與它相連的NMOS管導通,與它相連的PMOS管截止,輸出為低電平;僅當A、B全為低電平時(shí),兩個(gè)并聯(lián)NMOS管都截止,兩個(gè)串聯(lián)的PMOS管都導通,輸出為高電平。

因此,這種電路具有或非的邏輯功能,其邏輯表達式為L(cháng)=A+B顯然,n個(gè)輸入端的或非門(mén)必須有n個(gè)NMOS管并聯(lián)和n個(gè)PMOS管并聯(lián)。

比較CMOS與非門(mén)和或非門(mén)可知,與非門(mén)的工作管是彼此串聯(lián)的,其輸出電壓隨管子個(gè)數的增加而增加;或非門(mén)則相反,工作管彼此并聯(lián),對輸出電壓不致有明顯的影響。因而或非門(mén)用得較多。

聯(lián)系方式:鄒先生

聯(lián)系電話(huà):0755-83888366-8022

手機:18123972950

QQ:2880195519

聯(lián)系地址:深圳市福田區車(chē)公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關(guān)注”官方微信公眾號

請“關(guān)注”官方微信公眾號:提供 ?MOS管 ?技術(shù)幫助